Graphics Gremlin HDMI

Graphics Gremlin HDMI by Yeo Kheng Meng (yeokm1)

Project: https://github.com/yeokm1/graphics-gremlin-hdmi

This is a modified version of the Graphics Gremlin ISA CGA/MDA graphics card to include a HDMI port.

This is still based on the same Lattice ICE40HX4K FPGA.

The latest revision now displays CGA colour 6 brown correctly. Since this project builds on the original project, it carries over some emulation inaccuracies in demos like 8088MPH and other applications.

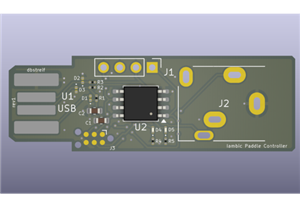

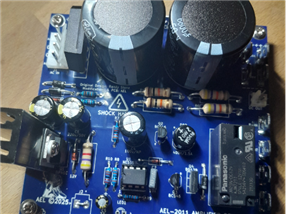

Top view of board

Left is the original Graphics Gremlin, right is my modified design.

Demo videos

Bootup and CGA compatibility tester (Brown fixed): https://www.youtube.com/watch?v=Ap-goSkkSUI

Bootup and CGA compatibility tester (Deprecated): https://www.youtube.com/watch?v=xLy6on_o4YM

8088MPH: https://www.youtube.com/watch?v=WLpNmEhdTe4

Area5150 (using CGA overscan): https://www.youtube.com/watch?v=9wYU6qMWlpE

My talk on this project: https://www.youtube.com/watch?v=r_GiEIe_oZk

Changes from original project

Hardware changes

- Added HDMI port by removing the RGBI DE9 port. Port positions adjusted to ease trace routing.

- Added TI TFP410 DVI transmitter (HDMI is compatible with DVI). HDMI is independent of the VGA/Composite output.

- Test points for inputs to DVI transmitter.

- Replaced the 3.3VDC 1A linear regulator with 3A as TFP410 is power hungry at up to 1A.

- Added pin headers for power.

- Added LED power indicators for 5V and 3.3V.

- 2-layer -> 4-layer board to ease routing.

HDL code changes

- Selectable MDA colours (HDMI only)

- Removed normal MDA bitstream as there is no more RGBI port.

- Added CGA 70Hz mode.

- Added CGA 60Hz overscan mode for demo and debug purposes.

- Modified Scandoubler code to support Display Enable signal as required by DVI chip but not VGA.

Readme of the original Graphics Gremlin project can be found here.

How to replicate this board and use it?

My IBM 5155 running the CGA Compatibility Tester displaying the colour palatte.

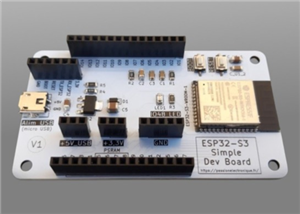

Testing with Mimas A7 (Xilinx Artix 7)

As part of my testing, I also made a small FPGA test project using another FPGA board Mimas A7 based on the Xilinx Artix 7.

Graphics Gremlin HDMI

*PCBWay community is a sharing platform. We are not responsible for any design issues and parameter issues (board thickness, surface finish, etc.) you choose.

- Comments(1)

- Likes(8)

-

Andrei Belov

Aug 13,2025

Andrei Belov

Aug 13,2025

-

Nigel Barink

Jun 02,2025

Nigel Barink

Jun 02,2025

-

Engineer

May 10,2025

Engineer

May 10,2025

-

Freddy Maes

Sep 29,2024

Freddy Maes

Sep 29,2024

-

Engineer

Sep 29,2024

Engineer

Sep 29,2024

-

Engineer

Jun 29,2024

Engineer

Jun 29,2024

-

Daniel Bergman

Jun 20,2024

Daniel Bergman

Jun 20,2024

-

(DIY) C64iSTANBUL

Jun 11,2024

(DIY) C64iSTANBUL

Jun 11,2024

- 0 USER VOTES

- YOUR VOTE 0.00 0.00

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

More by ExPLIT Laboratories

More by ExPLIT Laboratories

-

Radio 86RK - ROM Cartridge by Sergey Kiselev

Project: https://github.com/skiselev/radio-86rk-rom

Radio 86RK - ROM Cartridge by Sergey Kiselev

Project: https://github.com/skiselev/radio-86rk-rom

-

Radio 86RK by Sergey Kiselev

Project: https://github.com/skiselev/radio-86rk

Radio 86RK by Sergey Kiselev

Project: https://github.com/skiselev/radio-86rk

-

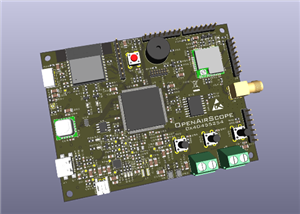

GBDSO - Gameboy Digital Sampling Oscilloscope by pyroesp

Project: https://github.com/pyroesp/GBDSO

GBDSO - Gameboy Digital Sampling Oscilloscope by pyroesp

Project: https://github.com/pyroesp/GBDSO

-

Graphics Gremlin HDMI

Graphics Gremlin HDMI by Yeo Kheng Meng (yeokm1)Project: https://github.com/yeokm1/graphics-gremlin-...

Graphics Gremlin HDMI

Graphics Gremlin HDMI by Yeo Kheng Meng (yeokm1)Project: https://github.com/yeokm1/graphics-gremlin-...

-

-

mammoth-3D SLM Voron Toolhead – Manual Drill & Tap Edition

148 0 0 -

-

AEL-2011 Power Supply Module

664 0 2 -

AEL-2011 50W Power Amplifier

571 0 2 -

-

-

Custom Mechanical Keyboard

771 0 0 -

Tester for Touch Screen Digitizer without using microcontroller

402 2 2 -

Audio reactive glow LED wristband/bracelet with NFC / RFID-Tags

366 0 1 -

-