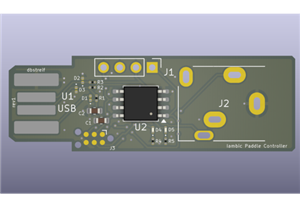

SBC-85 Expansion Memory Board

New for Version 1.0a The 'access' LEDs are now latched so they extend for one bus read cycle, i.e., they turn on when the memory site is first accessed and then turn off upon the next RD or WR strobe. This should prevent the false illumination seen in version 1.0 but they will still glow with varying brightness depending upon the frequency of access. Also, the backwards D5 and missing bPAS status bit have been corrected.

Features:

The board has four memory sockets and will accept any combination of 2732, 2764, 27128, or 27256 EPROMs or 6264 RAM chips. This gives a fully populated up to 128KB of ROM, or 32KB RAM, or anywhere in between. The type of chip is selected by a combination of three jumpers to define pins 1, 26, and 27 of the socket to match the pinout of the device.

The memory device flexibility results in a memory mapping problem of how to decode the memory space when the four positions each can have different chips and different memory space lengths. Having discrete logic and jumpers for the memory spaces would be extremely difficult and switching to programmable gates is a non-starter for most users.

To solve the memory mapping problem and adapt to different chips of different size, each socket is given its own memory reservation option via jumpers. This does take a little more user understanding, but the SBC-85 seems to have brilliant users so I am not too worried about that. In practice, the user will set the base address being careful, as with any memory board, to make sure that none of the address selections overlap. To accommodate the various address block length for each chip, rather than just a “match address =0” or “match address =1” the user has three choices for the jumpers on address lines A15 to A12: address = 0, address = 1, or address = don’t care.

For example– If the user wants to install a 2732 at address 0x8000. Since this is a 2732 which is 4KB, the memory block will go from 0x8000 to 0x8FFF so the user will select A15=1, A14=0, A13=0, A12=0. If the next chip is also a 2732 and the user wants contiguous memory the next 2732 will have the jumpers set to 0x9000, i.e., A15=1, A14=0, A13=0, A12=1 and so forth. This example is the simplest because the EPROM takes all the space between the address options, i.e., setting A15-A12 alone claims the necessary address space.

However, when a larger chip is used, the least of the four address bits needs to be set to “don’t care” in order to claim sufficient address space. If the user wants to use a pair of 16kB 27128s, just looking at the number of address lines on the chip (A0->A13 = 14) tells us we can only use A15 and A14 to select the chip because A13 and A12 are part of the chip’s memory block. So for the first 27128 at 0x8000 the jumpers will be set to A15=1, A14=0, A13=don’t care, A12=don’t care. The next 27128 up would be set for 0xC000 A15=1, A14=1, A13 & A12 = Don’t Care again. While relatively simple the trade off is, of course, that the larger chips must start on an even boundary of their block size.

This addressing scheme essentially breaks the memory board down into four separately located memory blocks of the appropriate size for the selected chip. In the end, with a little bit of planning one or more of these boards can be a contiguous block, so no need to reassemble or recompile around memory gaps.

Finally, since the board obviously exceeds the addressable address space, there are three additional selection bits PA0, PA1, and PA2 which can be defined. The board has a 3-bit I/O port select register to set these three page address bits to turn the selected devices on or off. For example, if the user has selected 000 for these three using the jumpers, then that device is only enabled when the user has cleared those three bits in the board’s select register via an OUT instruction. Using the ‘Don’t Care” bits, allows any of the four memory devices to span more than one selection, i.e., a board with PA2=1, PA1=1 and PA0=”Don’t Care” will be enabled when either 110 or 111 is sent to the board select register. Setting all the jumpers to “Don’t Care” essentially removes this feature so there is one less thing to worry about.

DESIGN NOTE: I am a bit disappointed with the 'ACCESS' LEDs on version 1.0. To keep the board this size, these LEDs are driven from the P=Q output of the address match circuit for that specific memory chip and not gated by the IO/M or the WR and RD signals. As a result, they illuminate when any transient address match is on the bus. If the address selection for that memory site is small, they work well enough. But as the site takes a larger and larger block so there are more "don't cares" in the address range, the LED tends to turn on too much as it starts to see more transient addresses in the "don't care" space. If I had gated this signal with the specific RD or WR* signal for that site, the LED would be ON such a small length of time it would have been difficult to see. In the next version of this board, I need to reconsider attempting to make these LEDs only illuminate for the exact site match and then latch them for that bus cycle so they stay on long enough to be visible. Until then, I give the 'access' LEDs a score of 3/10 for usefulness.

See the SBC-85 project website for additional information and documentation

SBC-85 Expansion Memory Board

*PCBWay community is a sharing platform. We are not responsible for any design issues and parameter issues (board thickness, surface finish, etc.) you choose.

- Comments(0)

- Likes(0)

- 0 USER VOTES

- YOUR VOTE 0.00 0.00

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

More by Craig

More by Craig

-

STD Bus Pad Per Hole Prototyping Board

Some 45 years later the STD Bus remains a great platform for vintage computer hobbyists. This protot...

STD Bus Pad Per Hole Prototyping Board

Some 45 years later the STD Bus remains a great platform for vintage computer hobbyists. This protot...

-

STD Bus 8085 Single Board computer

The STD Bus was one of the greatest industrial busses of all time, was incredibly flexible, enjoyed ...

STD Bus 8085 Single Board computer

The STD Bus was one of the greatest industrial busses of all time, was incredibly flexible, enjoyed ...

-

SBC-85 Expansion Memory Board

New for Version 1.0a The 'access' LEDs are now latched so they extend for one bus read cycle, i.e., ...

SBC-85 Expansion Memory Board

New for Version 1.0a The 'access' LEDs are now latched so they extend for one bus read cycle, i.e., ...

-

SBC-85 Serial- Parallel I/O board

The board has four I/O devices:An Intel 8255 PPI which provides three, 8-bit programmable I/O ports;...

SBC-85 Serial- Parallel I/O board

The board has four I/O devices:An Intel 8255 PPI which provides three, 8-bit programmable I/O ports;...

-

SBC-85 1Mbit Magnetic Bubble Memory Board

1 Megabit magnetic bubble memory board addition to the SBC-85 FamilyNOTE: This board is for the 20-p...

SBC-85 1Mbit Magnetic Bubble Memory Board

1 Megabit magnetic bubble memory board addition to the SBC-85 FamilyNOTE: This board is for the 20-p...

-

SBC-3870 Development board for Mostek 38P70 F8 processor

The 38P70 is the 2nd Generation of the original Fairchild F8.This is a PROTOTYPE board, it has been ...

SBC-3870 Development board for Mostek 38P70 F8 processor

The 38P70 is the 2nd Generation of the original Fairchild F8.This is a PROTOTYPE board, it has been ...

-

SBC-85 v2 Single Board 8085 Computer

New for version 2.0 (see video) are two universal EPROM sockets provide 2x2732, 2x2764, 2x27128, or ...

SBC-85 v2 Single Board 8085 Computer

New for version 2.0 (see video) are two universal EPROM sockets provide 2x2732, 2x2764, 2x27128, or ...

-

SBC-85 8085 Bus Monitor with Single Step, Binary and Hexadecimal display, Breakpoints

Short of an in circuit emulator, the bus monitor is one of the most powerful diagnostic tools.The bu...

SBC-85 8085 Bus Monitor with Single Step, Binary and Hexadecimal display, Breakpoints

Short of an in circuit emulator, the bus monitor is one of the most powerful diagnostic tools.The bu...

-

SBC-85 Cassette Tape Data Storage Interface Board

Among the standard cassette tape interfaces like Tarbell and the Kansas City, Intel developed an int...

SBC-85 Cassette Tape Data Storage Interface Board

Among the standard cassette tape interfaces like Tarbell and the Kansas City, Intel developed an int...

-

SBC-85 Pad-per-hole Prototyping Board

One tool for a healthy hardware user group is the ability for the users to create, invent, and contr...

SBC-85 Pad-per-hole Prototyping Board

One tool for a healthy hardware user group is the ability for the users to create, invent, and contr...

-

SBC-85 Backplane-4

The 8085 based SBC-85 was designed with an expansion bus having all 16 bits of the address, data bit...

SBC-85 Backplane-4

The 8085 based SBC-85 was designed with an expansion bus having all 16 bits of the address, data bit...

-

8085 Single Board Computer System SBC-85 CPU v1.1

This version has been updated to SBC-85 v2 which has universal EPROM sockets and other enhancements....

8085 Single Board Computer System SBC-85 CPU v1.1

This version has been updated to SBC-85 v2 which has universal EPROM sockets and other enhancements....

-

-

mammoth-3D SLM Voron Toolhead – Manual Drill & Tap Edition

136 0 0 -

-

AEL-2011 Power Supply Module

643 0 2 -

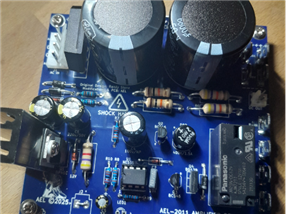

AEL-2011 50W Power Amplifier

560 0 2 -

-

-

Custom Mechanical Keyboard

762 0 0 -

Tester for Touch Screen Digitizer without using microcontroller

392 2 2 -

Audio reactive glow LED wristband/bracelet with NFC / RFID-Tags

361 0 1 -

-